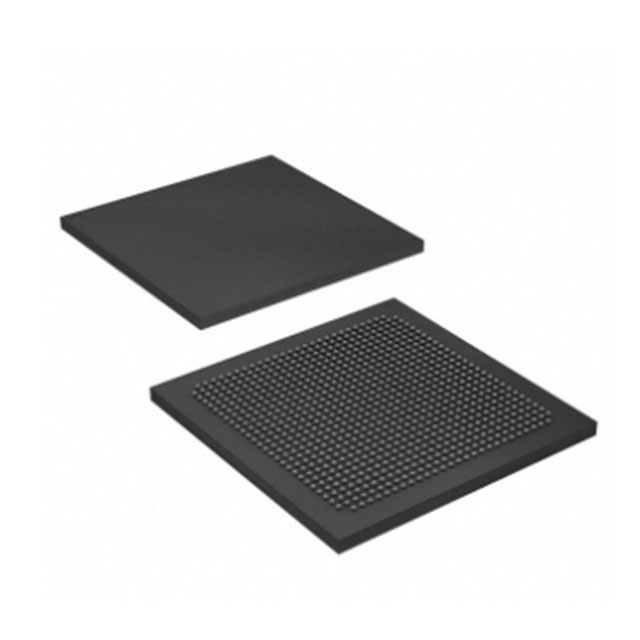

5CEFA5F23I7N Cyclone® VE Field Programmable Gate Array (FPGA) IC 240 5001216 77000 484-BGA

Produit Attributer

| TYPE | ILLUSTRÉIERT |

| Kategorie | Field Programmable Gate Arrays (FPGAs) |

| Fabrikant beschwéiert | Intel |

| Serie | Cyclone® VE |

| ëmklammen | Schacht |

| Produit Status | Aktiv |

| DigiKey ass programméierbar | Net verifizéiert |

| LAB/CLB Nummer | 29 080 |

| Zuel vun Logik Elementer / Unitéiten | 77000 |

| Gesamtzuel vun RAM Bits | 5001216 |

| I/O 數 | 240 |

| Spannung - Energieversuergung | 1.07V~1.13V |

| Installatioun Typ | Uewerfläch Klebstoff Typ |

| Operatioun Temperatur | -40°C ~ 100°C(TJ) |

| Package / Wunnengen | 484-BGA |

| Verkeefer Komponent encapsulation | 484-FBGA (23x23) |

| Produit Meeschtesch Zuel | 5CEFA5 |

Produit Aféierung

D'Cyclone® V-Geräter sinn entwéckelt fir gläichzäiteg de schrumpfende Stroumverbrauch, d'Käschte an d'Zäit-ze-Maart Ufuerderunge z'empfänken;an d'Erhéijung vun der Bandbreedungsfuerderunge fir héichvolumen a kaschtempfindlech Uwendungen.Verstäerkt mat integréierten Transceiver an Hard Memory Controller, sinn d'Cyclone V Geräter gëeegent fir Uwendungen an den industriellen, drahtlose a Kabel, Militär an Autosmäert.

Produit Fonctiounen

Technologie

- TSMC's 28-nm Low-Power (28LP) Prozesstechnologie

- 1,1 V Kär Volt

Verpakung

- Wirebond Low-Halogen Packagen

- Multiple Gerätsdichte mat kompatiblen Package Footprints fir eng nahtlos Migratioun tëscht verschiddenen Apparatdensitéiten

- RoHS-konform a gefouert Optiounen

Héich-Performance FPGA Stoff

- Verbesserte 8-Input ALM mat véier Registere

Intern Erënnerung spären

- M10K—10-Kilobits (Kb) Erënnerungsblocken mat mëllen Fehlerkorrekturcode (ECC)

- Memory Logic Array Block (MLAB) - 640-Bit verdeelt LUTRAM wou Dir bis zu 25% vun den ALMs als MLAB Memory benotze kënnt

Embedded Hard IP Blocks

- Native Ënnerstëtzung fir bis zu dräi Signalveraarbechtungspräzisniveauen (dräi 9 x 9, zwee 18 x 18 oder een 27 x 27 Multiplikator) am selwechte Variabel-Präzisioun DSP Block

- 64-Bit Akkuen a Kaskade

- Embedded intern Koeffizient Erënnerung

- Preadder / Subtractor fir verbessert Effizienz

- DDR3, DDR2, an LPDDR2 mat 16 an 32 Bit ECC Ënnerstëtzung

- PCI Express* (PCIe*) Gen2 a Gen1 (x1, x2 oder x4) schwéier IP mat Multifunktiounssupport, Endpunkt a Rootport

Configuratioun

- Amper Schutz - ëmfaassend Designschutz fir Är wäertvoll IP Investitiounen ze schützen

- Erweidert fortgeschratt Verschlësselungsstandard (AES) Design Sécherheetsfeatures

- CvP

- Dynamesch Rekonfiguratioun vun der FPGA

- Aktiv Serial (AS) x1 an x4, passiv Serial (PS), JTAG, a séier passiv parallel (FPP) x8 an x16 Konfiguratiounsoptiounen

- Intern Schrauwen (2)

- Deelweis Rekonfiguratioun (3)

Schreift äre Message hei a schéckt en un eis