Brand nei éierleche IC Stock Elektronesch Komponenten Ic Chip Support BOM Service TPS62130AQRGTRQ1

Produit Attributer

| TYPE | BESCHREIWUNG |

| Kategorie | Integréiert Circuits (ICs) |

| Mfr | Texas Instrumenter |

| Serie | Automotive, AEC-Q100, DCS-Control™ |

| Package | Tape & Reel (TR) Cut Tape (CT) Digi-Reel® |

| SPQ | 250T&R |

| Produit Status | Aktiv |

| Funktioun | Schrëtt-Down |

| Ausgang Configuratioun | Positiv |

| Topologie | Buck |

| Ausgang Typ | Upassbar |

| Zuel vun Ausgänge | 1 |

| Spannung - Input (Min) | 3V |

| Spannung - Input (Max) | 17 V |

| Spannung - Ausgang (Min/Fix) | 0, 9v |

| Spannung - Ausgang (Max) | 6V |

| Aktuell - Ausgang | 3A |

| Frequenz - Wiesselen | 2,5 MHz |

| Synchrone Rectifier | Jo |

| Operatioun Temperatur | -40°C ~ 125°C (TJ) |

| Montéierung Typ | Surface Mount |

| Package / Fall | 16-VFQFN ausgesat Pad |

| Fournisseur Apparat Package | 16-VQFN (3x3) |

| Basis Produit Zuel | TPS62130 |

1.

Wann mir wësse wéi den IC konstruéiert ass, ass et Zäit ze erklären wéi et ze maachen.Fir eng detailléiert Zeechnung mat enger Spraydous vu Lack ze maachen, musse mir eng Mask fir d'Zeechnen ausschneiden an op Pabeier setzen.Dann sprëtzen mir d'Faarwen gläichméisseg op de Pabeier an huelt d'Mask aus, wann d'Faarf getrocknegt ass.Dëst gëtt ëmmer erëm widderholl fir en ordentlechen a komplexe Muster ze kreéieren.Ech sinn ähnlech gemaach, andeems ech Schichten openeen an engem Maskéierungsprozess stackelen.

D'Produktioun vun ICs kann an dës 4 einfach Schrëtt opgedeelt ginn.Och wann déi tatsächlech Fabrikatiounsschrëtt variéiere kënnen an d'Materialien déi benotzt kënne variéieren, ass den allgemenge Prinzip ähnlech.De Prozess ass liicht anescht wéi Molerei, an deem ICs mat Lack hiergestallt ginn an dann maskéiert ginn, wärend Lack fir d'éischt maskéiert an dann gemoolt gëtt.All Prozess gëtt ënnendrënner beschriwwen.

Metal Sputtering: D'Metallmaterial fir ze benotzen ass gläichméisseg op de Wafer gesprëtzt fir en dënnen Film ze bilden.

Photoresist Applikatioun: D'Fotoresistmaterial gëtt als éischt op de Wafer geluecht, an duerch d'Fotomask (de Prinzip vun der Photomask gëtt d'nächst Kéier erkläert), gëtt de Liichtstrahl op den ongewollten Deel geschloen fir d'Struktur vum Photoresistmaterial ze zerstéieren.Dat beschiedegt Material gëtt dann mat Chemikalien ewechgewäsch.

Ätzen: De Siliziumwafer, deen net vum Photoresist geschützt ass, gëtt mat engem Ionestrahl geätzt.

Photoresist Entfernung: De verbleiwen Photoresist gëtt mat enger Photoresist Entfernungsléisung opgeléist, sou datt de Prozess ofgeschloss ass.

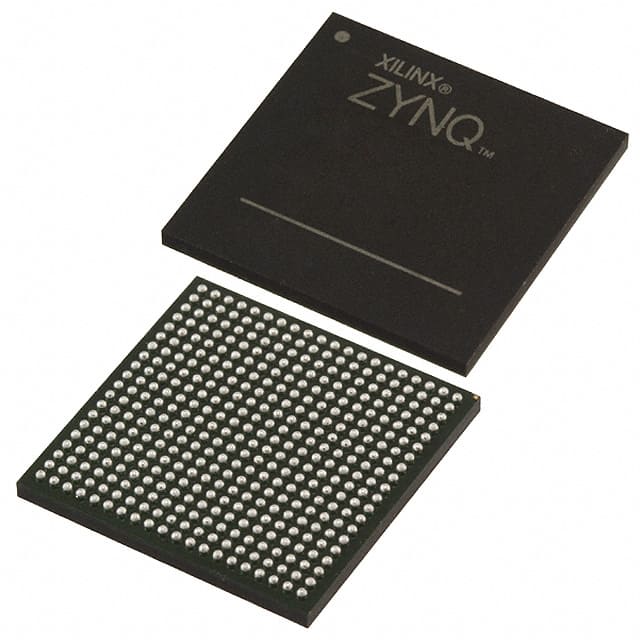

D'Finale Resultat ass e puer 6IC Chips op enger eenzeger Wafer, déi dann ausgeschnidden an an d'Verpackungsanlag geschéckt ginn fir ze packen.

2.Wat ass den Nanometer Prozess?

Samsung an TSMC kämpfen et am fortgeschrattene Halbleiterprozess, jidderee probéiert e Virsprong an der Schmelz ze kréien fir Bestellungen ze sécheren, an et ass bal eng Schluecht tëscht 14nm an 16nm ginn.A wat sinn d'Virdeeler an d'Problemer déi duerch de reduzéierte Prozess mat sech bruecht ginn?Drënner erkläre mir kuerz den Nanometer Prozess.

Wéi kleng ass en Nanometer?

Ier mer ufänken, ass et wichteg ze verstoen wat Nanometer bedeit.A mathematesche Begrëffer ass en Nanometer 0,000000001 Meter, awer dëst ass en zimlech schlecht Beispill - schliisslech kënne mir nëmmen e puer Nullen nom Dezimalpunkt gesinn, awer hu kee richtege Sënn vu wat se sinn.Wa mir dat mat der Dicke vun engem Fangerneel vergläichen, ass et vläicht méi offensichtlech.

Wa mir e Lineal benotze fir d'Dicke vun engem Nol ze moossen, kënne mir gesinn datt d'Dicke vun engem Nol ongeféier 0,0001 Meter (0,1 mm) ass, dat heescht datt wa mir probéieren d'Säit vun engem Nol an 100.000 Zeilen ze schneiden, all Zeil entsprécht ongeféier 1 Nanometer.

Wa mir wësse wéi kleng en Nanometer ass, musse mir den Zweck verstoen fir de Prozess ze schrumpfen.Den Haaptzweck fir de Kristall ze schrumpfen ass méi Kristalle an e méi klengen Chip ze passen, sou datt den Chip net méi grouss gëtt wéinst technologesche Fortschrëtter.Schlussendlech wäert déi reduzéiert Gréisst vum Chip et méi einfach maachen an mobilen Apparater ze passen an zukünfteg Nofro fir dënn ze treffen.

Huelt 14nm als Beispill, de Prozess bezitt sech op déi klengst méiglech Drotgréisst vu 14nm an engem Chip.