Nei an originell XC5VFX30T-2FFG665I Integréiert Circuit

Produit Attributer

| TYPE | BESCHREIWUNG | SELECT |

| Kategorie | Integréiert Circuits (ICs) |

|

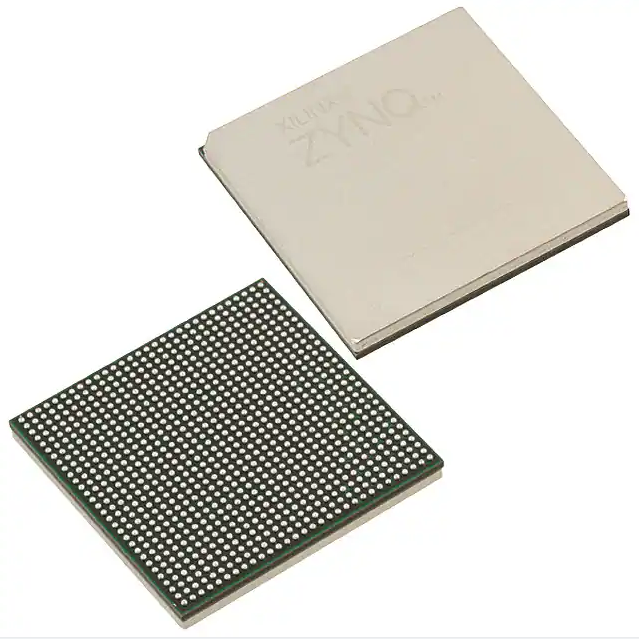

| Mfr | AMD Xilinx |

|

| Serie | Virtex®-5 FXT |

|

| Package | Schacht |

|

| Produit Status | Aktiv |

|

| Zuel vun LABs / CLBs | 2560 |

|

| Zuel vun Logik Elementer / Zellen | 32768 |

|

| Total RAM Bits | 2506752 |

|

| Zuel vun ech / O | 360 |

|

| Spannung - Versuergung | 0,95 V ~ 1,05 V |

|

| Montéierung Typ | Surface Mount |

|

| Operatioun Temperatur | -40°C ~ 100°C (TJ) |

|

| Package / Fall | 665-BBGA, FCBGA |

|

| Fournisseur Apparat Package | 665-FCBGA (27×27) |

|

| Basis Produit Zuel | XC5VFX30 |

|

Rapport Produit Informatiounen Feeler

View Ähnlech

Dokumenter & Medien

| RESOURCE TYPE | LINK |

| Datenblätter | Virtex-5 Famill Iwwersiicht |

| Ëmwelt- Informatiounen | Xilinx REACH211 Cert |

| PCN Design / Spezifizéierung | Kräiz-Schëff Lead-gratis Notiz 31/okt/2016 |

Ëmwelt- & Export Klassifikatiounen

| ATRIBUTE | BESCHREIWUNG |

| RoHS Status | ROHS3 konform |

| Moisture Sensitivity Level (MSL) | 4 (72 Stonnen) |

| REACH Status | REACH Onbeaflosst |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Feldprogramméierbar Gate Array

AFeldprogramméierbar Gate Array(FPGA) ass anintegréiert Circuitentworf fir vun engem Client oder engem Designer no der Fabrikatioun konfiguréiert ze ginn - also de BegrëffFeldprogramméierbar.D'FPGA Konfiguratioun gëtt allgemeng spezifizéiert mat engemHardware Beschreiwung Sprooch(HDL), ähnlech wéi déi benotzt fir engApplikatioun-spezifesch integréiert Circuit(ASIC).Circuit Diagrammerware virdru benotzt fir d'Konfiguratioun ze spezifizéieren, awer dëst ass ëmmer méi rar wéinst dem Advent vunelektronesch Design AutomatisatiounTools.

FPGAs enthalen eng Rei vunprogramméierbar logesch Blocks, an eng Hierarchie vun rekonfiguréierbaren Interconnects, déi et erlaabt datt d'Blocke matenee verbonne sinn.Logik Blocks kënne konfiguréiert ginn fir komplex ze maachenkombinéiert Funktiounen, oder handelen esou einfachlogesch PaartegärANanXOR.An de meeschte FPGAs enthalen och LogikblockenErënnerung Elementer, wat einfach ka sinnflip-flopsoder méi komplett Erënnerungsblocken.[1]Vill FPGAs kënnen nei programméiert ginn fir verschidden ëmzesetzenlogesch Funktiounen, erlaabt flexibelreconfigurable Rechenzäitwéi duerchgefouert anComputer Software.

FPGAs hunn eng bemierkenswäert Roll anembedded SystemEntwécklung wéinst hirer Kapazitéit fir System Software Entwécklung gläichzäiteg mat Hardware unzefänken, System Performance Simulatioune an enger ganz fréier Phase vun der Entwécklung z'erméiglechen, an erlaben verschidde System Tester an Design Iteratiounen ier d'Systemarchitektur finaliséiert ginn.[2]

Geschicht[änneren]

D'FPGA Industrie ass ausprogramméierbar liesen-nëmmen Erënnerung(PROM) anprogramméierbar Logik Geräter(PLDs).PROMs a PLDs haten allebéid d'Méiglechkeet fir a Chargen an enger Fabrik oder am Feld programméiert ze ginn (Feldprogramméierbar).[3]

Alteragouf 1983 gegrënnt an huet den éischte reprogramméierbare Logik-Apparat vun der Industrie am Joer 1984 geliwwert - den EP300 - deen eng Quarzfenster am Package huet, deen d'Benotzer erlaabt huet eng ultraviolet Lampe op der Stierwen ze blénken fir d'Läschen ze läschen.EPROMZellen déi d'Apparatkonfiguratioun ofgehalen hunn.[4]

Xilinxproduzéiert déi éischt kommerziell liewensfäeg Feld-programméierbarGate Arrayam Joer 1985[3]- XC2064.[5]Den XC2064 hat programméierbar Paarte a programméierbar Verbindungen tëscht Paarte, den Ufank vun enger neier Technologie a Maart.[6]Den XC2064 hat 64 konfiguréierbar Logikblocken (CLBs), mat zwee dräi-InputBléck Dëscher(LUT).[7]

1987 huet deNaval Surface Warfare Centerfinanzéiert en Experiment proposéiert vum Steve Casselman fir e Computer z'entwéckelen deen 600.000 reprogramméierbar Paarte ëmsetzen.Casselman war erfollegräich an e Patent am Zesummenhang mam System gouf 1992 ausgestallt.[3]

Altera an Xilinx weider onerfueren a séier vun 1985 bis Mëtt-1990er gewuess wann Konkurrenten Spross, e groussen Deel vun hirem Maart Undeel eroded.Bis 1993, Actel (eloMikrosemi) war ongeféier 18 Prozent vum Maart servéiert.[6]

D'1990er waren eng Period vu schnelle Wuesstum fir FPGAs, souwuel am Circuit Raffinesséierung wéi och am Volume vun der Produktioun.Am fréien 1990er goufen FPGAs haaptsächlech benotzt anTelekommunikatiounanVernetzung.Um Enn vum Joerzéngt hunn FPGAs hire Wee an de Konsument, Automotive an Industrieanwendungen fonnt.[8]

Bis 2013 hunn Altera (31 Prozent), Actel (10 Prozent) an Xilinx (36 Prozent) zesummen ongeféier 77 Prozent vum FPGA Maart vertrueden.[9]

Firmen wéi Microsoft hunn ugefaang FPGAs ze benotzen fir héich performant, computationell intensiv Systemer ze beschleunegen (wéi deDaten Zentrendéi hir BedreiwenBing Sichmotor), wéinst derLeeschtung pro WattVirdeel FPGAs liwweren.[10]Microsoft huet ugefaang FPGAs ze benotzen firbeschleunegenBing am Joer 2014, an am Joer 2018 huet ugefaang FPGAs iwwer aner Datenzenter Aarbechtslaascht z'installéieren fir hirAzur Cloud RechenzäitPlattform.[11]

Déi folgend Timeline weisen Fortschrëtter a verschiddenen Aspekter vum FPGA Design un:

Gates

- 1987: 9.000 Paarte, Xilinx[6]

- 1992: 600.000, Naval Surface Warfare Departement[3]

- Ufank 2000s: Millioune[8]

- 2013: 50 Milliounen, Xilinx[12]

Maart Gréisst

- 1985: Éischt kommerziell FPGA : Xilinx XC2064[5][6]

- 1987: $ 14 Milliounen[6]

- c.1993: > $ 385 Milliounen[6][gescheitert Verifizéierung]

- 2005: 1,9 Milliarden Dollar[13]

- 2010 Schätzungen: $ 2,75 Milliarden[13]

- 2013: $ 5,4 Milliarden[14]

- 2020 Schätzung: $ 9,8 Milliarde[14]

Design fänkt un

ADesign ufänkenass en neie personaliséierten Design fir Implementatioun op enger FPGA.

Design[änneren]

Zäitgenëssesch FPGAs hu grouss Ressourcen vunlogesch Paartea RAM-Blöcke fir komplex digital Berechnungen ëmzesetzen.Als FPGA Designs benotze ganz séier I / O Tariffer a bidirektional DatenBussen, gëtt et eng Erausfuerderung fir de korrekten Timing vu gültege Donnéeën bannent Setup-Zäit ze verifizéieren an Zäit ze halen.

Buedem Planungerméiglecht d'Ressourceallokatioun bannent FPGAs fir dës Zäitbeschränkungen ze treffen.FPGAs kënne benotzt ginn fir all logesch Funktioun ëmzesetzen, déi enASICLeeschtunge kann.D'Kapazitéit fir d'Funktionalitéit nom Versand ze aktualiséieren,partiell Re-Configuratiounvun engem Deel vum Design[17]an déi niddreg net widderhuelend Ingenieurskäschte relativ zu engem ASIC Design (trotz den allgemeng méi héije Eenheetskäschte), bidden Virdeeler fir vill Uwendungen.[1]

E puer FPGAs hunn analog Funktiounen zousätzlech zu digitale Funktiounen.Déi meescht üblech Analog Feature ass programméierbarschlëmmen Tauxop all Ausgangspin, wat den Ingenieur erlaabt niddereg Tariffer op liicht gelueden Pins ze setzen déi soss géifenringoderKoppelinakzeptabel, a méi héich Tariffer op schwéier gelueden Pins op Héich-Vitesse Channels ze setzen, déi soss ze lues lafen.[18][19]Och heefeg sinn Quarz-Kristalloszilléierer, On-Chip Resistenz-Kapazitéit Oszilléierer, anPhase-gespaarten Schleifenmat agebonnenSpannungskontrolléiert Oszilléiererbenotzt fir Auer Generatioun a Gestioun souwéi fir Héich-Vitesse serializer-deserializer (SERDES) Iwwerdroung clocks an Receiver Auer Erhuelung.Zimlech heefeg sinn differentiellVergläicherop Input Pins entworf fir verbonne ginndifferentiell SignalisatiounChannels.E puer "gemëscht SignalFPGAs" hunn integréiert PeripherieAnalog-zu-Digital Konverter(ADCs) andigital-an-analog Konverter(DACs) mat analoge Signalkonditiounsblocken, déi hinnen erlaben als engSystem op engem Chip(SoC).[20]Esou Geräter verschwannen d'Linn tëscht enger FPGA, déi digital an Nullen op sengem internen programmierbaren Interconnect Stoff dréit, anFeldprogramméierbar analog Array(FPAA), déi analog Wäerter op sengem internen programméierbare Interconnect Stoff dréit.