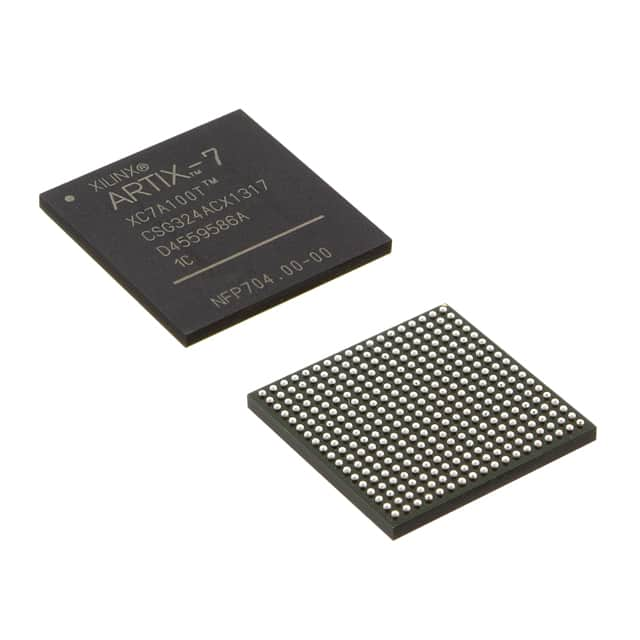

Original IC Chip Programméierbar XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Produit Attributer

| TYPE | BESCHREIWUNG |

| Kategorie | Integréiert Circuits (ICs) |

| Mfr | AMD Xilinx |

| Serie | Virtex® UltraScale™ |

|

| Këscht |

| Standard Package | 1 |

| Produit Status | Aktiv |

| Zuel vun LABs / CLBs | 316620 |

| Zuel vun Logik Elementer / Zellen | 5540850 |

| Total RAM Bits | 90726400 |

| Zuel vun ech / O | 1456 |

| Spannung - Versuergung | 0,922V ~ 0,979V |

| Montéierung Typ | Surface Mount |

| Operatioun Temperatur | -40°C ~ 100°C (TJ) |

| Package / Fall | 2892-BBGA, FCBGA |

| Fournisseur Apparat Package | 2892-FCBGA (55×55) |

| Basis Produit Zuel | XCVU440 |

Benotzt FPGAs als Verkéiersprozessor fir Netzwierksécherheet

Traffic op a vu Sécherheetsgeräter (Firewalls) gëtt op verschidde Niveauen verschlësselt, an L2 Verschlësselung / Entschlësselung (MACSec) gëtt an der Linkschicht (L2) Netzknäppchen (Schalter a Router) veraarbecht.Veraarbechtung iwwer d'L2 (MAC Layer) enthält typesch méi déif Parsing, L3 Tunnel Decryption (IPSec), a verschlësselte SSL Traffic mat TCP / UDP Traffic.Packet Veraarbechtung involvéiert d'Parsing an d'Klassifikatioun vun erakommen Paketen an d'Veraarbechtung vu grousse Verkéiersvolumen (1-20M) mat héijer Duerchgang (25-400Gb / s).

Wéinst der grousser Unzuel u Rechenressourcen (Kären) déi erfuerderlech sinn, kënnen NPUs fir relativ méi héijer Geschwindegkeet Paketveraarbechtung benotzt ginn, awer geréng Latenz, héich performant skalierbar Trafficveraarbechtung ass net méiglech well de Verkéier mat MIPS / RISC Cores veraarbecht gëtt a sou Cores plangen. baséiert op hir Disponibilitéit ass schwéier.D'Benotzung vun FPGA-baséiert Sécherheetsapparater kann dës Aschränkungen vun CPU an NPU-baséiert Architekturen effektiv eliminéieren.

Applikatioun-Niveau Sécherheet Veraarbechtung an FPGAs

FPGAs sinn ideal fir Inline Sécherheetsveraarbechtung an nächster Generatioun Firewalls well se erfollegräich de Besoin fir méi héich Leeschtung, Flexibilitéit a Low-latency Operatioun treffen.Zousätzlech kënnen FPGAs och Applikatiounsniveau Sécherheetsfunktiounen ëmsetzen, déi Rechenressourcen weider spuere kënnen an d'Performance verbesseren.

Gemeinsam Beispiller vun Uwendungssécherheetsveraarbechtung an FPGAs enthalen

- TTCP Offload Engine

- Regelméisseg Ausdrock passende

- Asymmetresch Verschlësselung (PKI) Veraarbechtung

- TLS Veraarbechtung

Nächst Generatioun Sécherheetstechnologien déi FPGAs benotzen

Vill existent asymmetresch Algorithmen si vulnérabel fir Kompromëss vu Quantecomputer.Asymmetresch Sécherheetsalgorithmen wéi RSA-2K, RSA-4K, ECC-256, DH, an ECCDH sinn am meeschte betraff vu Quantecomputer Techniken.Nei Implementatioune vun asymmetreschen Algorithmen an NIST Standardiséierung ginn exploréiert.

Aktuell Virschléi fir Post-Quanteverschlësselung enthalen d'Ring-on-Error Learning (R-LWE) Method fir

- Public Key Cryptography (PKC)

- Digital Ënnerschrëften

- Schlëssel Kreatioun

Déi proposéiert Ëmsetzung vun der ëffentlecher Schlësselkryptographie enthält verschidde bekannte mathematesch Operatiounen (TRNG, Gaussian Noise Sampler, polynomial Additioun, binär polynomial Quantifier Divisioun, Multiplikatioun, etc.).FPGA IP fir vill vun dësen Algorithmen ass verfügbar oder kann effizient implementéiert ginn mat FPGA Bausteng, wéi DSP an AI Motoren (AIE) an existent an nächst Generatioun Xilinx Apparater.

Dëse Wäissbuch beschreift d'Ëmsetzung vun der L2-L7 Sécherheet mat enger programméierbarer Architektur déi fir Sécherheetsbeschleunigung a Rand-/Zougängsnetzwierker an Next-Generatioun Firewalls (NGFW) an Enterprise-Netzwierker ofgesat ka ginn.