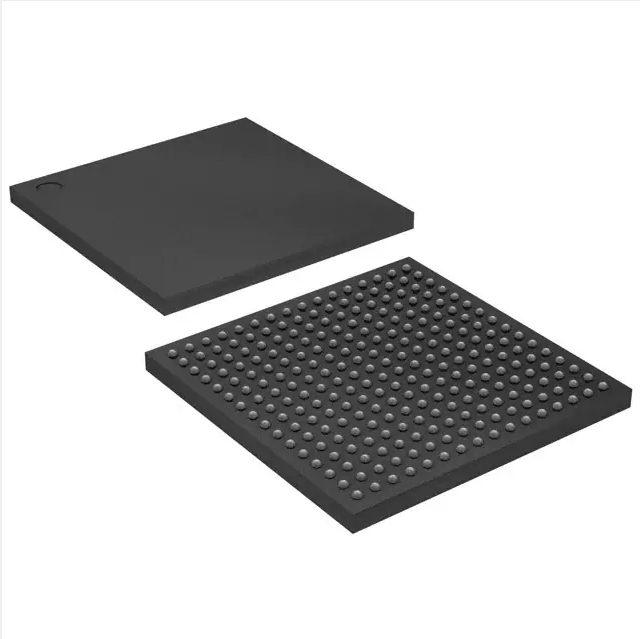

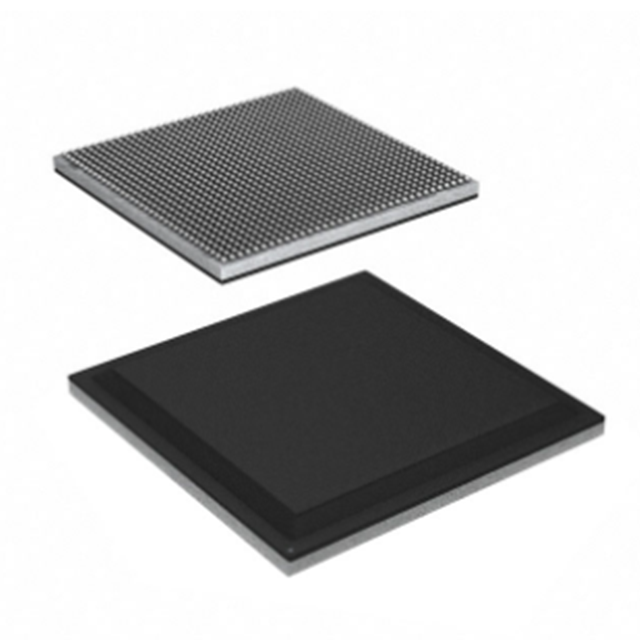

XCZU19EG-2FFVC1760E 100% Neien & Original DC Ze DC Konverter & Schaltregulator Chip

Produit Attributer

| Produit Attributer | Attribut Wäert |

| Hersteller: | Xilinx |

| Produit Kategorie: | SoC FPGA |

| Versandbeschränkungen: | Dëst Produkt kann zousätzlech Dokumentatioun erfuerderen fir aus den USA ze exportéieren. |

| RoHS: | Detailer |

| Montage Stil: | SMD/SMT |

| Package / Fall: | FBGA-1760 |

| Kär: | ARM Cortex A53, ARM Cortex R5, ARM Mali-400 MP2 |

| Zuel vu Cores: | 7 Kär |

| Maximal Auer Frequenz: | 600 MHz, 667 MHz, 1,5 GHz |

| L1 Cache Instruktioun Memory: | 2 x 32 kB, 4 x 32 kB |

| L1 Cache Data Memory: | 2 x 32 kB, 4 x 32 kB |

| Programm Memory Gréisst: | - |

| Daten RAM Gréisst: | - |

| Zuel vu Logik Elementer: | 1143450 LE |

| Adaptive Logik Moduler - ALMs: | 65340 ALM |

| Embedded Memory: | 34,6 Mbit |

| Betribssystemer Energieversuergung Volt: | 850 mV |

| Minimum Operatioun Temperatur: | 0 C |

| Maximal Operatioun Temperatur: | +100 C |

| Marke: | Xilinx |

| Verdeelt RAM: | 9,8 Mbit |

| Embedded Block RAM - EBR: | 34,6 Mbit |

| Feuchtigkeitempfindlech: | Jo |

| Zuel vu Logic Array Blocks - LABs: | 65340 LAB |

| Zuel vun Transceiver: | 72 Transceiver |

| Produit Typ: | SoC FPGA |

| Serie: | XCZU19EG |

| Factory Pack Quantitéit: | 1 |

| Ënnerkategorie: | SOC - Systemer op engem Chip |

| Handelsnumm: | Zynq UltraScale+ |

Integréiert Circuit Typ

Am Verglach mat Elektronen hunn Photonen keng statesch Mass, schwaach Interaktioun, staark Anti-Interferenzfäegkeet, a si méi gëeegent fir Informatiounsiwwerdroung.Optesch Interkonnektioun gëtt erwaart d'Kärtechnologie ze ginn fir d'Energieverbrauchsmauer, d'Späichermauer an d'Kommunikatiounsmauer duerchzebriechen.Illuminant, coupler, modulator, waveguide Apparater sinn integréiert an der héich Dicht opteschen Fonctiounen wéi photoelectric integréiert Mikro System, kann Qualitéit realiséieren, Volumen, Muecht Konsum vun héich Dicht photoelectric Integratioun, photoelectric Integratioun Plattform dorënner III - V Verbindung semiconductor monolithic integréiert (INP) ) passiv Integratioun Plattform, Silikat oder Glas (planar opteschen Waveguide, PLC) Plattform a Silicon-baséiert Plattform.

InP Plattform gëtt haaptsächlech fir d'Produktioun vu Laser, Modulator, Detektor an aner aktive Geräter benotzt, niddereg Technologieniveau, héich Substratkäschte;Benotzt PLC Plattform fir passiv Komponenten ze produzéieren, niddereg Verloscht, grousse Volumen;De gréisste Problem mat béide Plattformen ass datt d'Materialien net mat Silizium-baséiert Elektronik kompatibel sinn.De prominentste Virdeel vun der Silizium-baséierter photonescher Integratioun ass datt de Prozess kompatibel ass mam CMOS-Prozess an d'Produktiounskäschte sinn niddereg, sou datt et als déi potenziell optoelektronesch a souguer all-optesch Integratiounsschema ugesi gëtt.

Et ginn zwou Integratiounsmethoden fir Silizium-baséiert photonesch Geräter a CMOS Circuits.

De Virdeel vun der fréierer ass datt d'photonesch Apparater an elektronesch Geräter separat optimiséiert kënne ginn, awer déi spéider Verpakung ass schwéier a kommerziell Uwendungen si limitéiert.Déi lescht ass schwéier ze designen an d'Integratioun vun deenen zwee Apparater ze veraarbechten.Am Moment ass Hybridversammlung baséiert op Nuklearpartikelintegratioun déi bescht Wiel