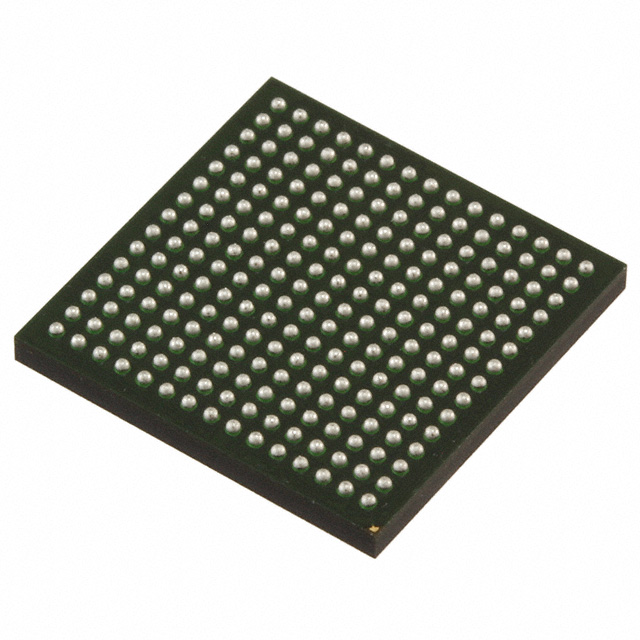

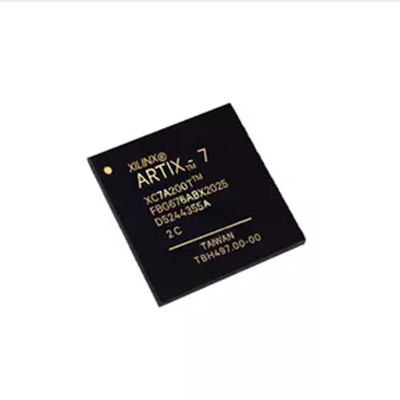

XC7Z007S-1CLG225I IC SOC CORTEX-A9 667MHZ 225BGA Elektronik Komponenten IC Chips integréiert Circuits eege Stock BOM Service

Produit Attributer

| TYPE | BESCHREIWUNG |

| Kategorie | Integréiert Circuits (ICs) |

| Mfr | AMD Xilinx |

| Serie | Zynq®-7000 |

| Package | Schacht |

| Standard Package | 160 |

| Produit Status | Aktiv |

| Architektur | MCU, FPGA |

| Kär Prozessor | Single ARM® Cortex®-A9 MPCore™ mat CoreSight™ |

| Flash Gréisst | - |

| RAM Gréisst | 256KB |

| Peripheriegeräter | DMA |

| Konnektivitéit | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed | 667 MHz |

| Primär Attributer | Artix™-7 FPGA, 23K Logik Zellen |

| Operatioun Temperatur | -40°C ~ 100°C (TJ) |

| Package / Fall | 225-LFBGA, CSPBGA |

| Fournisseur Apparat Package | 225-CSPBGA (13×13) |

| Zuel vun ech / O | 54 |

| Basis Produit Zuel | XC7Z007 |

China stëmmt AMD d'Acquisitioun vun Xilinx mat 5 Konditiounen!

De 27. Oktober 2020 huet AMD ugekënnegt datt et Xilinx (Xilinx) fir US $ 35 Milliarden an engem All-Aktien Deal kritt.Den Deal, wärend eestëmmeg vun de Verwaltungsrot vu béide Parteien guttgeheescht, muss nach ëmmer vun den Aktionäre vu béide Parteien guttgeheescht ginn, mat reglementaresche Genehmegung vu verschiddene Länner, dorënner natierlech China.

Viru kuerzem huet d'Anti-Monopoly Bureau of China's State Administration of Market Supervision and Administration d'Decisioun ugekënnegt fir d'Anti-Monopoly Iwwerpréiwung vun der Acquisitioun vun engem Akaf an Xilinx vun der Chaowei Semiconductor Corporation mat zousätzlech restriktiven Konditiounen (d'"Ukënnegung") ze stëmmen. d'Acquisitioun vu Xilinx vun AMD an d'Läschung vun der leschter reglementarescher Hürd fir d'Acquisitioun.

No der Ukënnegung, no engem Joer vun der Empfang vun der Anti-Monopol Deklaratioun vun der Bedreiwer Konzentratioun am Fall vun der AMD Acquisitioun vun Xilinx den 19. Januar 2021, an de Fall ofzeschléissen nodeems de Kandidat seng Erklärungsmaterial ergänzt huet, huet d'General Administration of Market Regulation (GAMR) huet decidéiert de Fall mat restriktive Konditiounen ze stëmmen.

Fusiounen sinn erlaabt, awer keng gebündelte Verkaf oder Diskriminatioun géint chinesesch Clienten

Et ass wichteg ze verstoen datt Acquisitioune mat grenziwwerschreidend Operatiounen reglementaresche Genehmegung vu verschiddene Schlësselmaartregulatorer ronderëm d'Welt erfuerderen.Virdrun haten d'USA, Groussbritannien an d'EU d'Acquisitioun scho geläscht, an elo datt China de Fall guttgeheescht huet, heescht et datt AMD seng Acquisitiounspläng am éischte Véierel vun 2022 fäerdeg bréngt.

Et sollt awer bemierkt ginn datt d'Zustimmung vun der AMD Acquisitioun vum Xilinx vun der chinesescher General Administration of Market Regulation mat zousätzlech restriktive Konditioune kënnt, déi béid Parteien vun der Transaktioun an der Post-Konzentratiounsentitéit erfuerderen déi folgend Obligatiounen ze erfëllen.

(i) Wann Dir SuperPower CPUs, SuperPower GPUs a Celeris FPGAs op de Maart a China verkaafen, da solle se op kee Fall gebonne Verkaf zwéngen oder aner onverständlech Handelsbedéngungen befestegt;si sollen d'Clienten net verhënneren oder beschränken déi uewe genannte Produkter individuell ze kafen oder ze benotzen;a si sollen net géint Clienten diskriminéieren déi uewe genannte Produkter individuell a punkto Serviceniveau, Präis, Softwarefeatures etc.

(b) Weider relevant Kooperatioun ze förderen baséiert op der existéierender Zesummenaarbecht mat Entreprisen a China a weider Chaowei CPUs, Chaowei GPUs, Xilinx FPGAs, a verbonne Software an Accessoiren op de Maart a China ze liwweren no de Prinzipien vu Fairness, raisonnabel an Net- Diskriminatioun.

(iii) Assuréieren d'Flexibilitéit an d'Programméierbarkeet vun den Xilinx FPGAs, weider ze entwéckelen an d'Disponibilitéit vun der Xilinx FPGA Produktlinn ze garantéieren, a sécherzestellen datt et op eng Manéier entwéckelt gëtt kompatibel mat ARM-baséiert Prozessoren an am Aklang mat dem Xilinx seng Pläng virun der Transaktioun .

(iv) weiderhin d'Interoperabilitéit vu Chaowei CPUs, Chaowei GPUs a Celeris FPGAs op de Maart a China mat Drëtt-Partei CPUs, GPUs an FPGAs verkaaft ze garantéieren;den uewe genannte Niveau vun der Interoperabilitéit däerf net méi niddereg sinn wéi den Niveau vun der Interoperabilitéit vu Chaowei CPUs, Chaowei GPUs a Celeris FPGAs;Informatioun, Featuren a Proben am Zesummenhang mat der Interoperabilitéitsupgrade sollen der Drëtt Partei bannent 90 Deeg no der Upgrade CPU, GPU a FPGA Hiersteller geliwwert ginn.

(v) Maacht Moossname fir d'Informatioun vun den Drëtt-Partei CPU, GPU, an FPGA Hiersteller ze schützen a Vertraulechkeetsaccorde mat den Drëtt-Partei CPU, GPU, an FPGA Hiersteller ze maachen;späichert déi vertraulech Informatioun vun den Drëtt-Partei CPU, GPU, a FPGA Hiersteller an getrennten an géigesäitege exklusiv Hardwaresystemer.

.png)