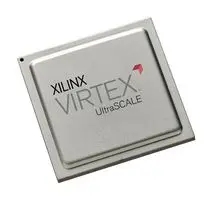

XCVU190-2FLGB2104I 100% Neien & Original Eegent Stock Integréiert Circuit High-Performance Clock Buffer Family

Produit Attributer

| TYPE | BESCHREIWUNG |

| Kategorie | FPGAs (Field Programmable Gate Array) |

| Mfr | AMD |

| Serie | Virtex® UltraScale™ |

| Package | Schacht |

| Produit Status | Aktiv |

| DigiKey Programméierbar | Net verifizéiert |

| Zuel vun LABs / CLBs | 134280 |

| Zuel vun Logik Elementer / Zellen | 2349900 |

| Total RAM Bits | 150937600 |

| Zuel vun ech / O | 702 |

| Spannung - Versuergung | 0,922V ~ 0,979V |

| Montéierung Typ | Surface Mount |

| Operatioun Temperatur | -40°C ~ 100°C (TJ) |

| Package / Fall | 2104-BBGA, FCBGA |

| Fournisseur Apparat Package | 2104-FCBGA (47.5x47.5) |

| Basis Produit Zuel | XCVU190 |

Beschreiwung

Kintex® UltraScale FPGAs: High-Performance FPGAs mat engem Fokus op Präis / Leeschtung, déi souwuel monolithesch wéi och nächst Generatioun stacked Silicon Interconnect (SSI) Technologie benotzen.Héich DSP a Block RAM-zu-Logik Verhältnisser an nächst Generatioun Transceiver, kombinéiert mat Low-Cost Verpackungen, erméiglechen eng optimal Mëschung vu Kapazitéit a Käschten.

Kintex UltraScale+ ™ FPGAs: Erhéicht Leeschtung an On-Chip UltraRAM Erënnerung fir BOM Käschten ze reduzéieren.Déi ideal Mëschung vun héich performant Peripherieger a kosteneffektive Systemimplementatioun.Kintex UltraScale + FPGAs hunn vill Kraaftoptiounen déi den optimale Gläichgewiicht tëscht der erfuerderter Systemleistung an der klengster Kraaft Enveloppe liwweren.

Virtex® UltraScale FPGAs: Héich-Kapazitéit, héich-Performance FPGAs aktivéiert souwuel monolithic an nächst Generatioun SSI Technologie benotzt.Virtex UltraScale Geräter erreechen déi héchst Systemkapazitéit, Bandbreedung a Leeschtung fir Schlësselmaart- an Uwendungsufuerderungen duerch Integratioun vu verschiddene Systemniveaufunktiounen unzegoen.

Virtex UltraScale + FPGAs: Déi héchste Transceiver Bandbreedung, héchste DSP Zuel, an héchsten On-Chip an In-Package Memory verfügbar an der UltraScale Architektur.Virtex UltraScale + FPGAs bidden och vill Kraaftoptiounen, déi den optimale Gläichgewiicht tëscht der erfuerderter Systemleistung an der klengster Kraaft Enveloppe liwweren.

Zynq® UltraScale+ MPSoCs: Kombinéiert den ARM® v8-baséiert Cortex®-A53 héich performant energieeffizienten 64-Bit Applikatiounsprozessor mam ARM Cortex-R5 Echtzäitprozessor an der UltraScale Architektur fir déi éischt All Programméierbar MPSoCs vun der Industrie ze kreéieren.Bitt onendlech Kraaftspueren, heterogen Veraarbechtung a programméierbar Beschleunegung.Zynq® UltraScale+ RFSoCs: Kombinéiert RF-Datenkonverter-Subsystem a Forward Fehlerkorrektur mat industrieféierend programméierbar Logik an heterogener Veraarbechtungsfäegkeet. , Multi-Modus Cellular Radios a Kabelinfrastruktur.