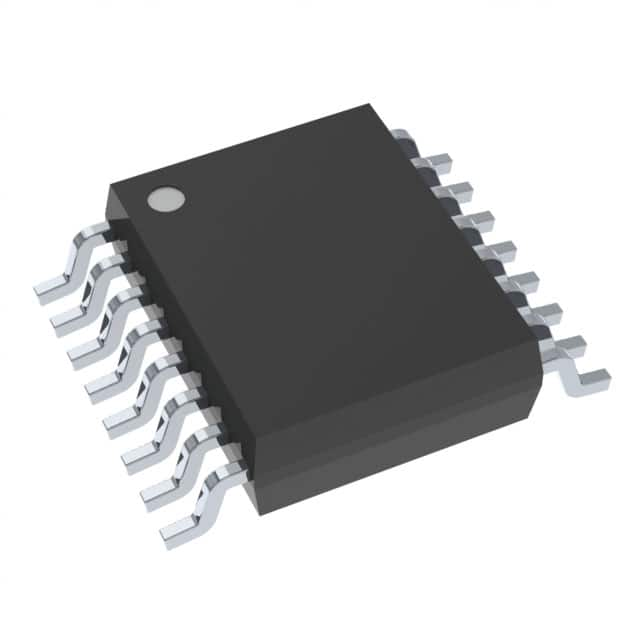

LM46002AQPWPRQ1 Package HTSSOP16 Integréiert Circuit IC Chip nei Original Spot Elektronik Komponenten

Produit Attributer

| TYPE | BESCHREIWUNG |

| Kategorie | Integréiert Circuits (ICs) |

| Mfr | Texas Instrumenter |

| Serie | Automotive, AEC-Q100, SIMPLE SWITCHER® |

| Package | Tape & Reel (TR) Cut Tape (CT) Digi-Reel® |

| SPQ | 2000T&R |

| Produit Status | Aktiv |

| Funktioun | Schrëtt-Down |

| Ausgang Configuratioun | Positiv |

| Topologie | Buck |

| Ausgang Typ | Upassbar |

| Zuel vun Ausgänge | 1 |

| Spannung - Input (Min) | 3, 5v |

| Spannung - Input (Max) | 60 v |

| Spannung - Ausgang (Min/Fix) | 1V |

| Spannung - Ausgang (Max) | 28v vun |

| Aktuell - Ausgang | 2A |

| Frequenz - Wiesselen | 200 kHz ~ 2,2 MHz |

| Synchrone Rectifier | Jo |

| Operatioun Temperatur | -40°C ~ 125°C (TJ) |

| Montéierung Typ | Surface Mount |

| Package / Fall | 16-TSSOP (0,173", 4,40 mm Breet) Exposéiert Pad |

| Fournisseur Apparat Package | 16-HTSSOP |

| Basis Produit Zuel | LM46002 |

Chip Produktioun Prozess

De komplette Chip Fabrikatiounsprozess enthält Chip Design, Wafer Produktioun, Chip Verpackung, an Chip Testen, dorënner de Wafer Produktiounsprozess besonnesch komplex.

Den éischte Schrëtt ass den Chip Design, deen op den Design Ufuerderunge baséiert, wéi funktionell Ziler, Spezifikatioune, Circuit Layout, Drot Wicklung an Detailer, etc.. D'"Design Zeechnungen" sinn generéiert;d'Fotomaske ginn am Viraus no den Chipregelen produzéiert.

②.Wafer Produktioun.

1. Silicon Wafers ginn op déi erfuerderlech Dicke geschnidden mat engem Wafer Slicer.Wat méi dënn de Wafer ass, wat méi niddereg d'Produktiounskäschte sinn, awer dest méi erfuerderlech de Prozess.

2. Beschichtung vun der Wafer Uewerfläch mat engem Photoresistfilm, wat d'Waferresistenz géint Oxidatioun an Temperatur verbessert.

3. Wafer Photolithographie Entwécklung an Ätzen benotzt Chemikalien, déi op UV Liicht sensibel sinn, dh si ginn méi mëll wann se UV Liicht ausgesat sinn.D'Form vum Chip kann duerch Kontroll vun der Positioun vun der Mask kritt ginn.E Photoresist gëtt op de Siliziumwafer applizéiert sou datt et opléist wann se un UV Liicht ausgesat ass.Dëst gëtt gemaach andeems Dir den éischten Deel vun der Mask applizéiert, sou datt den Deel, deen UV-Liicht ausgesat ass, opgeléist gëtt an dësen opgeléisten Deel kann dann mat engem Léisungsmëttel ewechgewäsch ginn.Dësen opgeléisten Deel kann dann mat engem Léisungsmëttel ofgewäsch ginn.De reschtlechen Deel gëtt dann wéi de Photoresist geformt, wat eis déi gewënschte Silikaschicht gëtt.

4. Injektioun vun Ionen.Mat enger Ätzmaschinn ginn d'N- a P Fallen an de bloe Silizium geätzt, an d'Ionen ginn injizéiert fir e PN-Kräizung ze bilden (Logikpaart);déi iewescht Metallschicht ass dann duerch chemesch a kierperlech Wieder Nidderschlag un de Circuit verbonnen.

5. Wafer Test No den uewe genannte Prozesser gëtt e Gitter vu Wierfel op der Wafer geformt.D'elektresch Charakteristike vun all Stierwen gi getest mat Pin Testen.

③.Chip Verpakung

De fäerdege Wafer ass fixéiert, mat Pins gebonnen, a verschidde Packagen no Nofro gemaach.Beispiller: DIP, QFP, PLCC, QFN, a sou weider.Dëst gëtt haaptsächlech duerch d'Applikatiounsgewunnechten vum Benotzer, d'Applikatiounsëmfeld, d'Maartsituatioun an aner periphere Faktoren bestëmmt.

④.Chip Testen

De finalen Prozess vun der Chipfabrikatioun ass fäerdeg Produkttesten, déi an allgemeng Tester a speziell Tester ënnerdeelt kënne ginn, de fréiere ass d'elektresch Charakteristiken vum Chip no der Verpakung a verschiddenen Ëmfeld ze testen, sou wéi Stroumverbrauch, Operatiounsgeschwindegkeet, Spannungsresistenz, asw.De speziellen Test baséiert op den technesche Parameteren vun de spezielle Besoinen vum Client, an e puer Chips aus ähnlechen Spezifikatioune a Varietéit ginn getest fir ze kucken ob se dem Client seng speziell Besoinen entspriechen, fir ze entscheeden ob speziell Chips fir de Client entworf ginn.Produkter, déi den allgemengen Test gepackt hunn, gi mat Spezifikatioune, Modellnummeren, a Fabrécksdatum markéiert a verpackt ier se d'Fabréck verlassen.Chips, déi den Test net passéieren, ginn als downgradéiert oder verworf ofhängeg vun de Parameteren, déi se erreecht hunn, klasséiert.

.png)